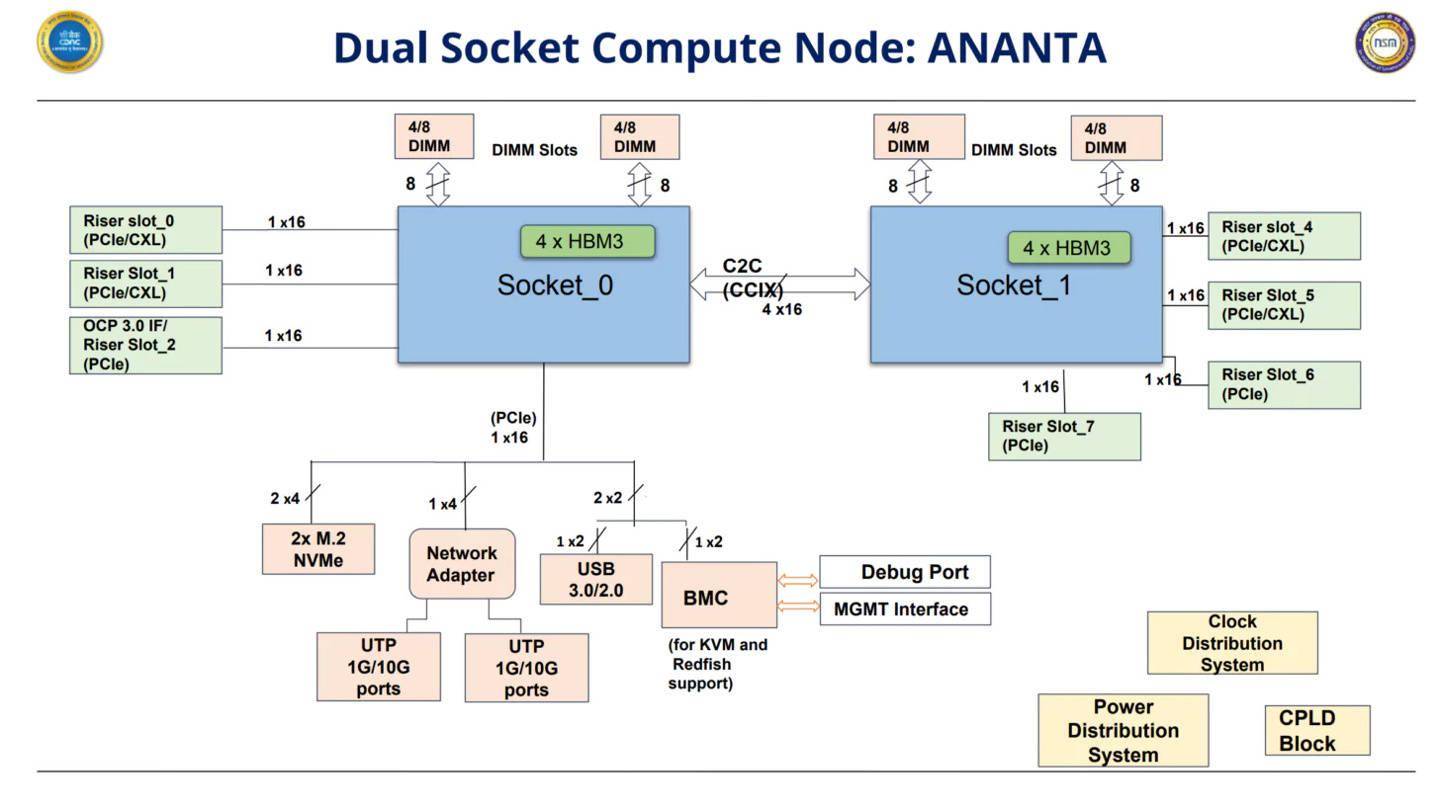

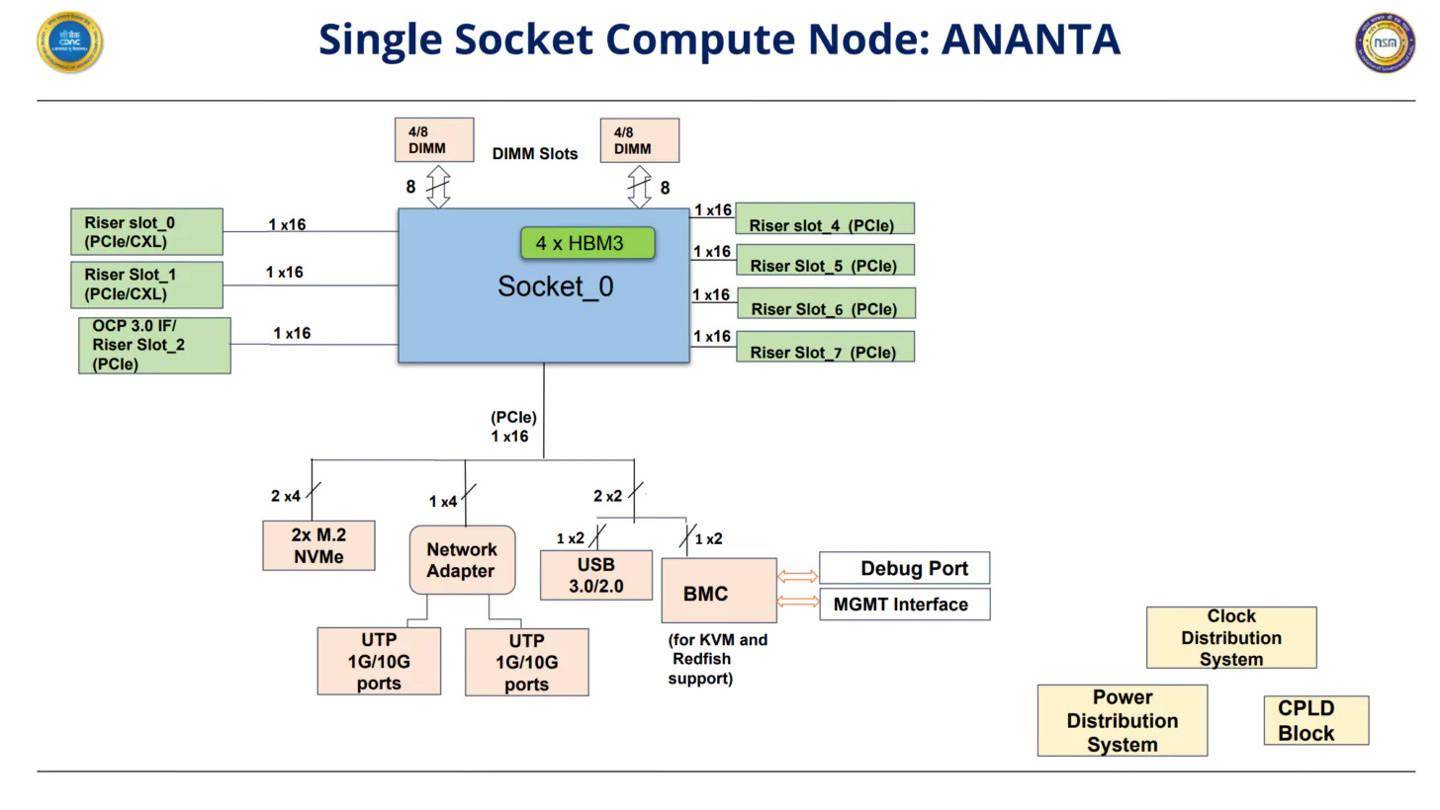

据介绍,这款旗舰芯片有着 96 个 ARM 内核、96 GB HBM3、128 个 PCIe Gen 5 通道,TDP 可达 320W。

C-DAC 表示,他们正在为国内应用开发多种选择,覆盖智能设备、物联网、AR / VR 到高性能计算和数据中心等领域。

C-DAC 的 Vega 系列 CPU 基于双核和四核设计,目标客户是需要低功耗和低成本芯片的入门级客户,预计将至少满足印度 10% 的芯片需求。此外,该公司还准备在未来三年内推出八核芯片,作为 Dhruv 和 Dhanush Plus 芯片的后续产品。

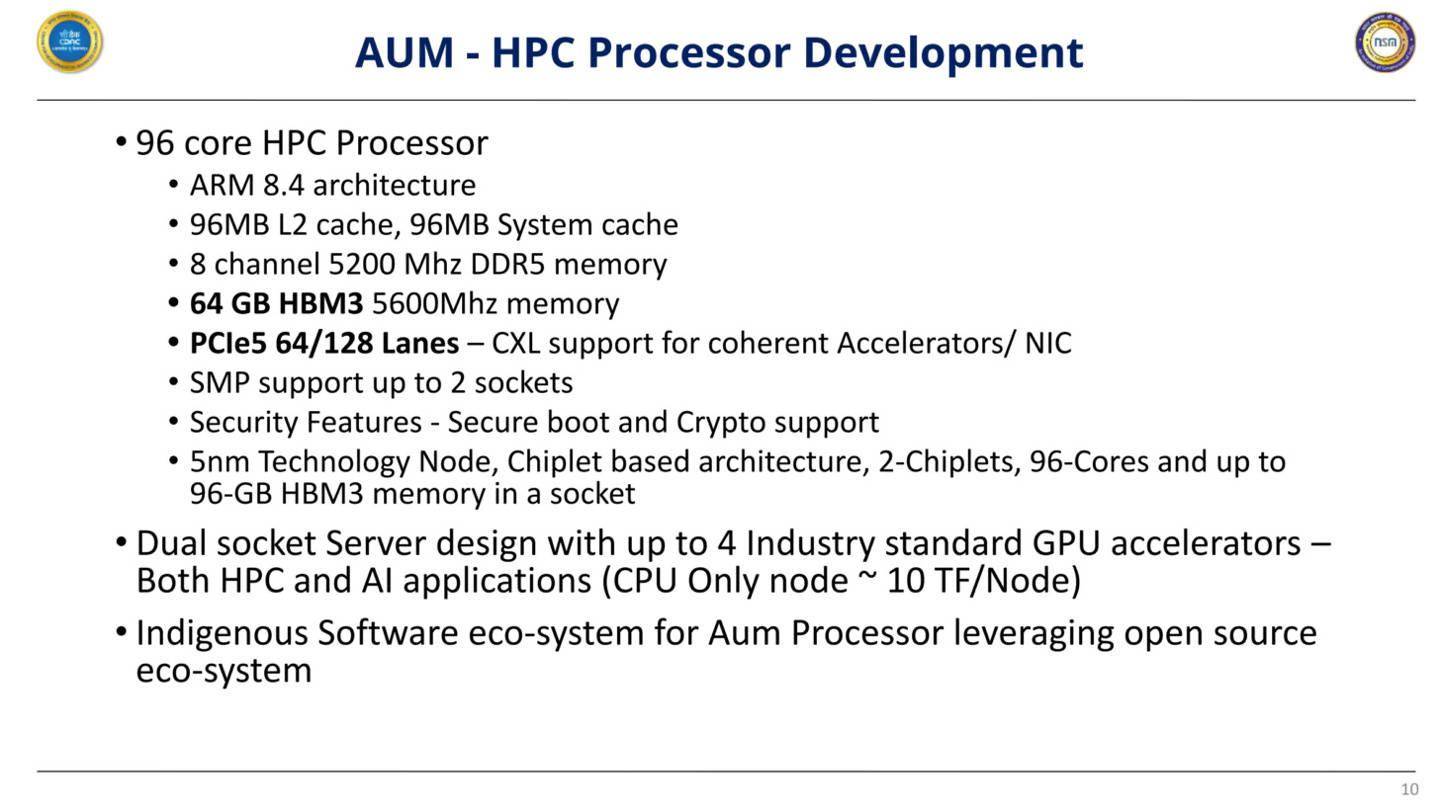

但这还不是全部,该公司现宣布正在研发一款非常节能的高性能计算芯片。作为印度国家超级计算任务 (NSM) 计划的一部分,该芯片将针对大规模工作负载,也就是 C-DAC AUM 处理器。

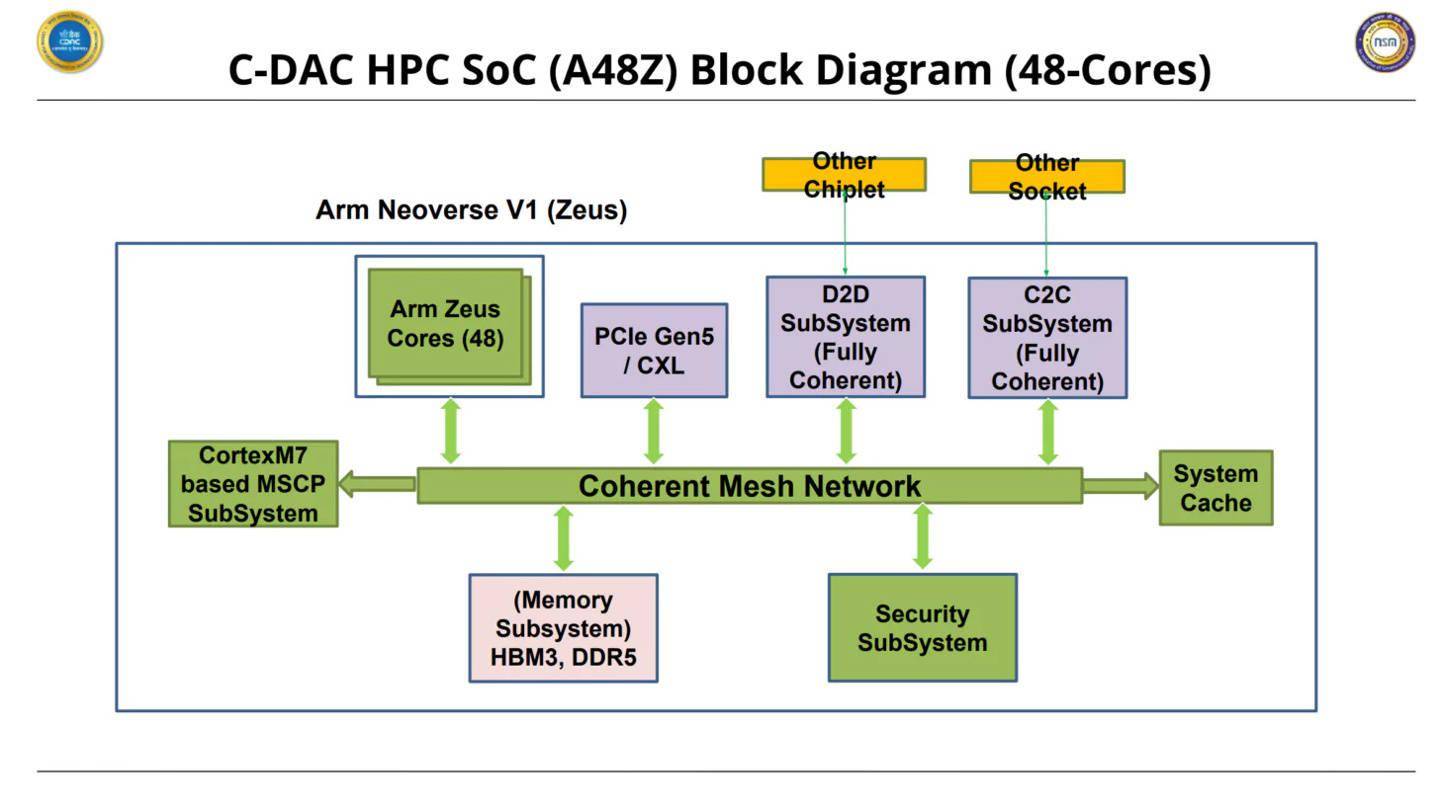

C-DAC AUM 基于代号为 Zeus 的 ARM Neoverse V1 架构,共有 96 个内核,但分为两个小芯片,每个小芯片包含 48 个 V1 内核。其中,每个芯片都有自己的内存、I / O、C2C / D2D 互连、缓存、安全和 MSCP 子系统部分。

据介绍,他们将这两个基于 a48z 的小芯片在同一中间层上使用 D2D 互连架构连接在一起。每个芯片还携带 96 MB 的二级缓存和 96 MB 的系统缓存。

此外,C-DAC AUM 使用了 64 GB 的 HBM3-5600 内存,同时还封装了 96 GB HBM3 内存和 8 通道 DDR5-5200 内存(注:最高可扩展至 16 通道,总带宽达 332.8 GB / s )。

得益于三重内存子系统设计,该 CPU 将承载 64/128 条 PCIe Gen 5 通道,支持 CXL,并在可包含其中两个芯片的平台上运行。

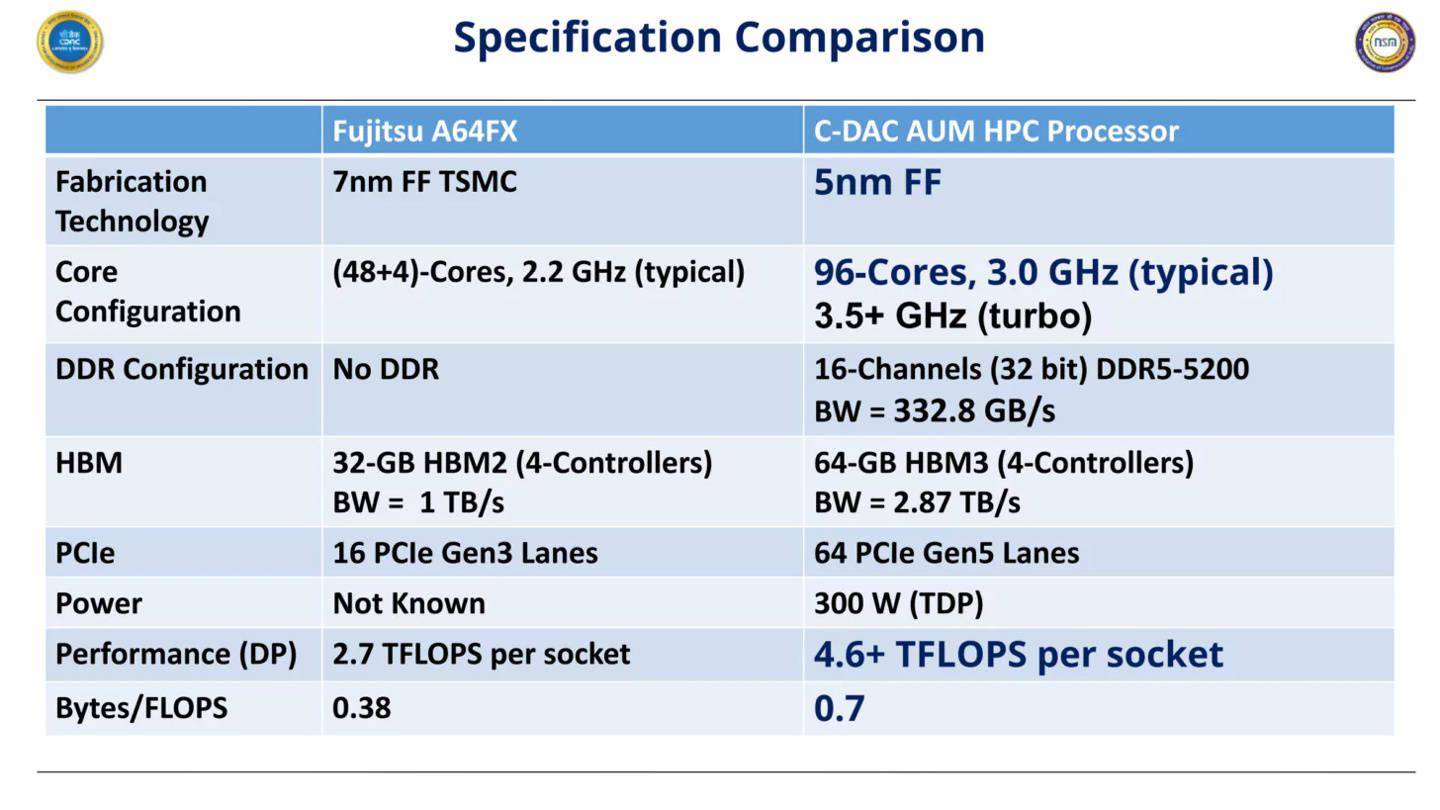

这款 CPU 将基于台积电 5nm 工艺制造,频率大约在 3.0 - 3.5 GHz 之间,纯 CPU 节点将提供高达每个节点 10 TFLOPs 的性能,每个插槽可带来 4.6+ TFLOPs 算力,而如果是双插槽服务器设计则可以支持最多 4 个标准 GPU 加速器。

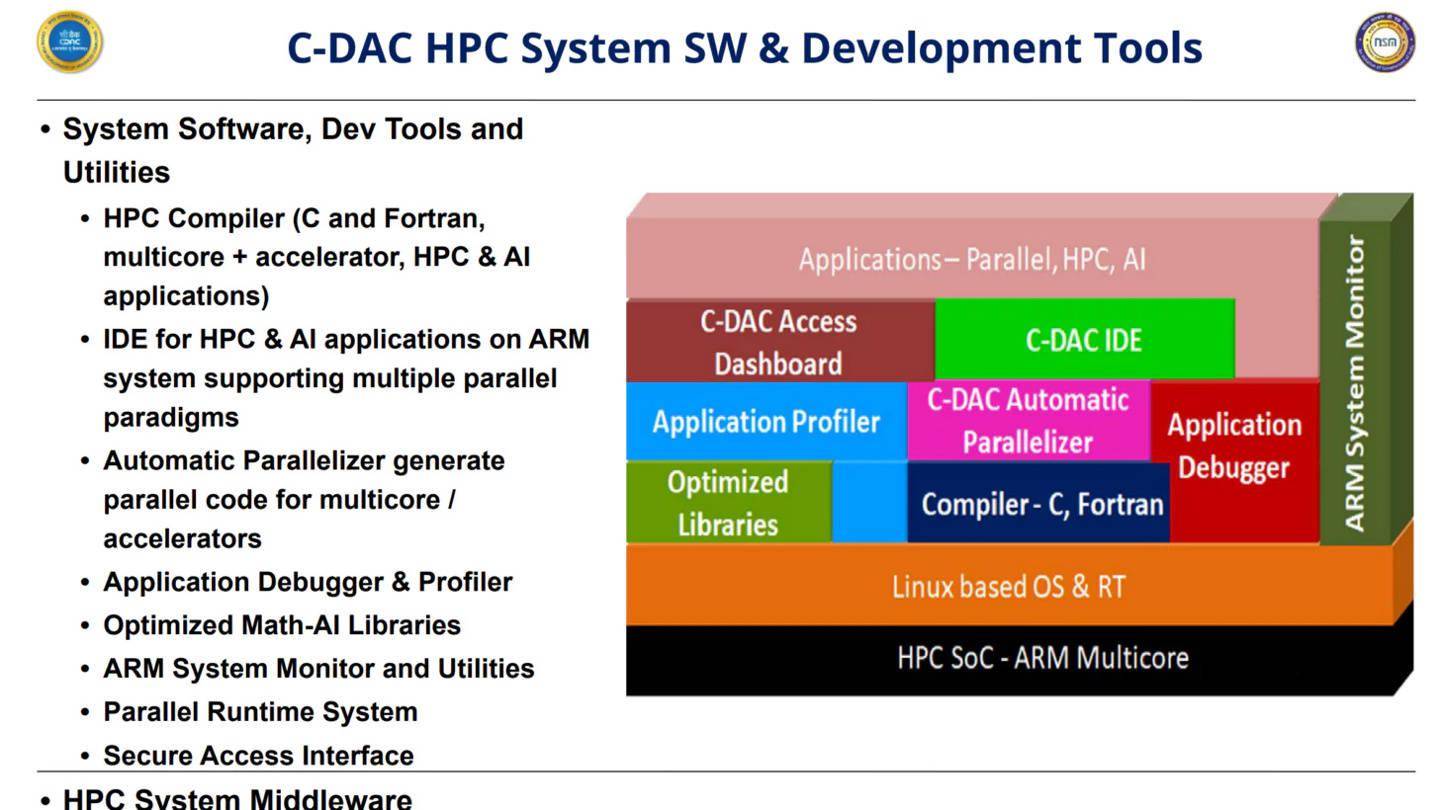

C-DAC 表示,他们还将准备一套 HPC 系统软件和开发工具,以充分发挥其硬件的潜力。该公司预计到 2024 年底将在印度本土实现 64 PetaFlops 的算力,而 AUM 芯片预计将在 2023-2024 年上市。